Traditional full-chip ATPGs are declining, and one of the main challenges for many existing and future integrated chip devices is how to create test patterns for a large number of designs. For designs with millions or even hundreds of millions of doors, it is impractical to traditionally design and recreate the test pattern. It takes a lot of computing power and considerable time to produce all of these patterns. The layered testability design solves this problem by performing DFT insertion and pattern generation on the block or kernel. This greatly reduces the pattern generation time and the computational resources required. It also allows you to complete most of the DFT and pattern generation ahead of the design process, dramatically improving predictability and reducing risk. This article introduces the layered DFT process: inserting a wrapper, generating a gray box image for the kernel, and redirecting the kernel-level pattern to a simple mapping step on top of the integrated chip.

Second, why is plug and play reasonable?

An important benefit of plug-and-play approach is that you can do everything ahead of the kernel level during the design process. This reduces many types of risks, as any problem can be resolved in advance, making the final chip test architecture and results more predictable. Doing more testing at the kernel level allows individual development teams to work independently and then deliver data such as standard DFT operations and test patterns to colleagues doing chip integration work. In addition, once the design and pattern data is complete, the same data can be reused for any chip design that uses the core. The plug-and-play approach is equally flexible. If there is a problem with the design and an engineering change (ECO) is required, then only the test pattern for the ECO core needs to be regenerated.

Third, use the wrapper chain to create a separate kernel

One of the basic requirements of the layered and kernel plug-and-play approach is to ensure that each core can be tested independently. The DFT tool can start from the core IO and traverse the kernel logic until the first register is found and then included in the wrapper chain. These units are called shared wrapper units because they perform both functional and test tasks. Many designs include register IO so that the timing of the signals entering and leaving the core can be well determined. This makes the wrapper insertion very easy.

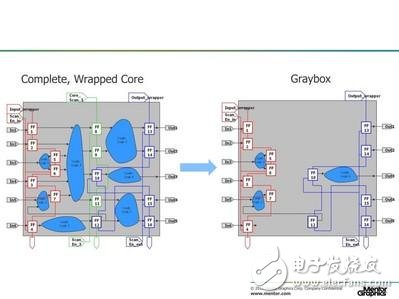

The wrapper chain also supports top-level IC modeling and rule checking. Once the wrapper chain is inserted, the DFT utility can analyze any kernel and find out what logic exists between the IO and the wrapper chain. Using this logic, part of the image of the kernel is written, which we call the gray box (Figure 1). The gray box is used to verify that the kernel is properly connected at the top level (design rule checking) and is also used to create simple interconnect tests between various cores.

Figure 1: When the scan chain is inserted into the kernel, the structure of the wrapper chain allows the kernel to be isolated as a complete wrapper kernel, as shown on the left. The image on the right shows a gray box model where the top level test only requires logic between the kernel IO and the wrapper chain.

Figure 1: When the scan chain is inserted into the kernel, the structure of the wrapper chain allows the kernel to be isolated as a complete wrapper kernel, as shown on the left. The image on the right shows a gray box model where the top level test only requires logic between the kernel IO and the wrapper chain.

Fourth, the kernel level of pattern generation

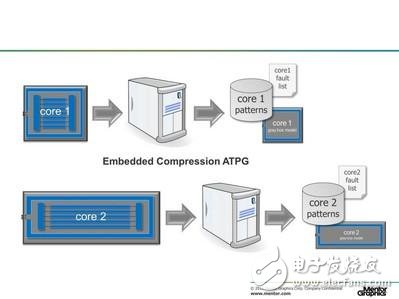

The advantage of hierarchical DFT is that the implementation of kernel DFT and ATPG can be completely independent of other cores (Figure 2). Even if the IO value is unknown, the wrapper chain enables ATPG to achieve high coverage. The ATPG tool only needs to get an indication that the test pattern will be redirected so that the unknown value can be assigned via IO and the appropriate data is stored. These appropriate data include any clock or constrained pins that need to be verified at the top of the IC.

Figure 2: Using the layered test approach, ATPG work for all blocks can be done independently on each core.

5. Redirect and integrate the kernel test pattern to the top layer

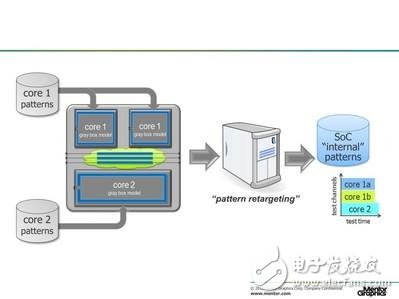

The layered DFT method facilitates the integration of test patterns for top-level ICs. The first step is to perform some basic DFT design rule checking (DRC). To complete this step, you only need a top-level netlist and a gray box model for all kernels (Figure 3). Hierarchical DFT methods often use the IC layer test access mechanism (TAM) to direct the IO of the chip to a particular block or block of blocks that need to be tested. It can be as simple as a few multiplexers or much more complex. Multiplexed cores typically have an input channel that is broadcast in parallel to all cores, so that the same test is obtained from a set of input channels. We recommend that TAM be based on IJTAG because IJTAG is a very broad and flexible standard and is best suited for plug and play.

Figure 3: Mode Redirection requires a separately generated kernel test pattern and redirects it so that it can be executed from the IC layer. This image shows the three kernel test patterns that were redirected and integrated, allowing them to execute in parallel. For a typical IC, there will be some blocks of test patterns integrated, while another part of the block needs to be put into another stage for testing.

Figure 3: Mode Redirection requires a separately generated kernel test pattern and redirects it so that it can be executed from the IC layer. This image shows the three kernel test patterns that were redirected and integrated, allowing them to execute in parallel. For a typical IC, there will be some blocks of test patterns integrated, while another part of the block needs to be put into another stage for testing.

The final step in the layering approach is to generate an IC layer test pattern that tests the interconnections between the cores. The gray box model is applied here. It is the ATPG step in the design phase because all kernel designs and TAM must first be completed before this.

What is the next step?

Basic features such as layered DFT scanning and wrapper insertion, gray box generation, and test pattern redirection provide a significant advantage for many designs. But which modules to choose for parallel testing and which serial tests to optimize test efficiency still require a lot of work. An effective top-level plan requires some kernel test pattern information to be valid. Similar to the ability to help determine the compression analysis for the best compression configuration, the top-level TAM planning is more efficient when the kernel design is available. One of the methods being developed for this problem is to dynamically allocate the IC channel bandwidth to each core. In this case, you do not need to know the nature of the kernel test pattern before designing the TAM. In addition, dynamically allocating the scan channel will reduce the size of the entire test pattern set.

Seven, the report summary

The layered DFT approach is being adopted by many designs, which significantly speeds up ATPG and reduces the size of the workstation. This is critical for ultra-large designs of hundreds of millions of gates or more. Another big advantage of layered DFT is that it greatly improves the process and brings the convenience of plug and play. Therefore, as long as the core design is complete, more DFT and ATPG work can be done at an earlier stage of the design cycle, which helps reduce risk, improve predictability, and later ECO.

ZGAR AZ CC Disposable

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

Our products include disposable e-cigarettes, rechargeable e-cigarettes, rechargreable disposable vape pen, and various of flavors of cigarette cartridges. From 600puffs to 5000puffs, ZGAR bar Disposable offer high-tech R&D, E-cigarette improves battery capacity, We offer various of flavors and support customization. And printing designs can be customized. We have our own professional team and competitive quotations for any OEM or ODM works.

We supply OEM rechargeable disposable vape pen,OEM disposable electronic cigarette,ODM disposable vape pen,ODM disposable electronic cigarette,OEM/ODM vape pen e-cigarette,OEM/ODM atomizer device.

Disposable E-cigarette, ODM disposable electronic cigarette, vape pen atomizer , Device E-cig, OEM disposable electronic cigarette

ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.szdisposable-vape.com