If a worker wants to do his job well, he must first sharpen his tools. Today's chip design has reached a billion-gate level of integration, and even the most experienced design engineers cannot complete it manually. In the chip design process, simulation verification is a very important link to ensure that the chip meets the expected design performance requirements before entering the tape-out production process. The EDA sub-industry, which provides simulation and verification tools for chip design engineers, is the most upstream and high-end node in the entire semiconductor industry ecological chain. The global EDA market is basically dominated by three companies: Cadence, Synopsys, and Mentor Graphics. Among them, the smallest Mentor Graphics has been acquired by Siemens. After more than 30 years of industry development and market competition, these three major EDA suppliers each have their own unique advantages and maintain a relatively balanced pattern in the dynamic changes of global semiconductor technology and market.

Cadence Protium verification platform shows off

AmLogic, which focuses on digital entertainment systems, recently launched a new multimedia system-on-chip (SoC), whose design cycle is shorter than the traditional design process by 2 months. In the highly competitive consumer electronics market, people in the industry should be very clear about what it means to launch new products 2 months earlier than their peers. The hero behind the realization of this chip design is the Protium S1 FPGA prototype verification platform from Cadence.

The newly launched Protium S1 is Cadence's FPGA-based prototype verification platform, and Jingchen is one of the early test participants of the verification platform. Benefiting from the platform’s unique design implementation and prototype verification acceleration capabilities, Jingchen can start the software development of SoC design earlier than ever.

According to Jerry Cao, director of software engineering at Jingchen Semiconductor, using the Protium S1 platform can execute multiple design examples at the same time, greatly improving productivity. In addition, the platform shares the same general compilation process with the Cadence Palladium Z1 enterprise-level hardware simulation accelerator, which can make full use of the existing Cadence verification environment, maintain functional consistency between platforms, and further improve design efficiency.

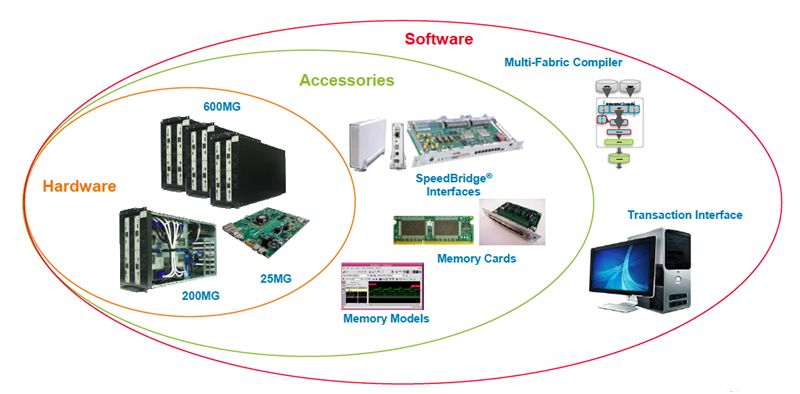

Figure 1: The complete suite of the Protium S1 platform

At the recent Shenzhen New Product Press Conference, Shi Fengyu, Global Vice President of Cadence, and Michal Siwinski, Vice President of Product Management and Operations of the System and Verification Division, introduced in detail the company's new FPGA prototype verification platform. The Protium S1 platform has the following performance advantages:

1. High-speed prototype design: The Protium S1 platform has advanced storage unit modeling and implementation capabilities, which can reduce the start-up time of prototype design from several months to several days, which greatly advances the firmware development schedule.

2. Innovative software debugging capabilities: The Protium S1 platform provides a variety of functions to improve firmware and software productivity, including backdoor reading and writing of storage units, cross-division dump waveforms, force-release statements, and run clock control.

3. Easy to use and deploy: The Protium S1 platform and Palladium Z1 share a common compilation process. The existing compilation environment has a repetitive utilization rate of up to 80%, and the front-end process can be highly consistent between the two platforms.

Protium S1 adopts Xilinx Virtex Ultra Scale FPGA technology, the design capacity is 6 times higher than the previous generation platform, and the performance is 2 times higher. It is consistent with the front end of the Cadence Palladium Z1 enterprise-level simulation platform, which makes the initial design start-up speed 80% higher than that of the traditional FPGA prototype platform. In addition to Jingchen Semiconductor, Protium S1 has been adopted by many manufacturers in the network, consumer and storage markets. Believe that in large-scale SoC design, it will become the right assistant of chip design engineers.

Parallel simulation has become the mainstream of EDA design this year

Driven by hardware simulation and FPGA prototype verification, verification in a software environment has become one of the key growth areas of EDA. The chip development process increasingly needs to consider the specific needs of specific applications. Today, a major theme in the field of EDA design is the "Internet of Things (IoT)." The Internet of Things spans multiple application areas, including wearable electronic products connected to mobile devices, smart homes connected to set-top boxes, connected car applications such as driver assistance systems (ADAS) and vehicle interconnection, as well as smart industries for automation, Healthcare, urban and energy management, etc.

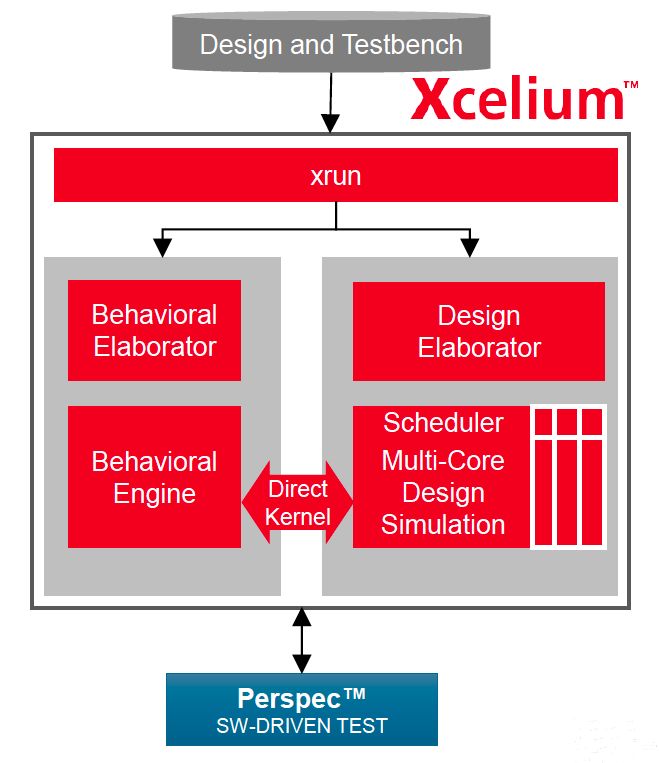

The four core engines for design verification include simulation, formal verification, hardware accelerator, and FPGA prototype verification. In addition to continuing to improve these core engines, parallel simulation has also become the mainstream trend of EDA this year. To meet this design requirement, Cadence introduced Xcelium, a parallel simulation platform based on multi-core parallel computing technology.

Xcelium is the third-generation parallel simulation platform that has passed product tapeout verification. The performance of its single-core version can be increased by an average of 2 times compared with the previous generation of Cadence simulation platform, and the performance of the multi-core version can be increased by more than 5 times on average. This parallel simulation platform can greatly accelerate system development and shorten the design time of system-on-chip (SoC). Its main highlights are as follows:

1. Multi-core simulation: Xcelium is derived from the technology brought by Rocketick acquired by Cadence, and is a parallel simulation platform based on product tapeout. The use of Xcelium can significantly shorten the execution time. The average speed of the register transfer level (RTL) simulation can be increased by 3 times, the gate level simulation can be increased by 5 times, and the DFT simulation can be increased by 10 times, saving project time from weeks to months.

2. Wide application: Xcelium supports a variety of design methods and IEEE standards, engineers can improve performance without recoding.

3. Easy to use: Xcelium's compilation process assigns the design and verification test environment code to the optimal engine, and automatically selects the optimal number of CPU cores to improve execution speed.

4. Adopt a number of patented technologies: New technologies to optimize the entire SoC verification time include System Verilog Testbench coverage and multi-core parallel compilation for rapid verification convergence.

Figure 2: Xcelium's parallel simulation architecture

The Xcelium simulation platform is suitable for mobile, imaging, servers, consumer electronics, Internet of Things (IoT) and automobiles. It has been successfully applied to early users such as ARM and ST, and has passed product tape-out verification. Hobson Bullman, general manager of ARM's technical service product department, said that the Xcelium parallel simulation platform can achieve a 4 times performance improvement in gate-level simulation for ARM-based SoC designs, and a 5 times performance improvement in RTL simulation. Based on the results of these early trials, he believes that Xcelium can help ARM and its customers deliver complex SoCs faster and more reliably.

"For the complex 28nm FD-SOI SoC and ASIC designs in smart cars and industrial Internet of Things applications, fast and scalable simulation is the key to meeting the rigorous development cycle!" STMicroelectronics CPU team manager Francois Oswald said, "We Using the Cadence Xcelium parallel simulation platform, the serial mode DFT simulation is 8 times faster, so the digital and mixed-signal SoC verification team chose Xcelium as the standard simulation solution."

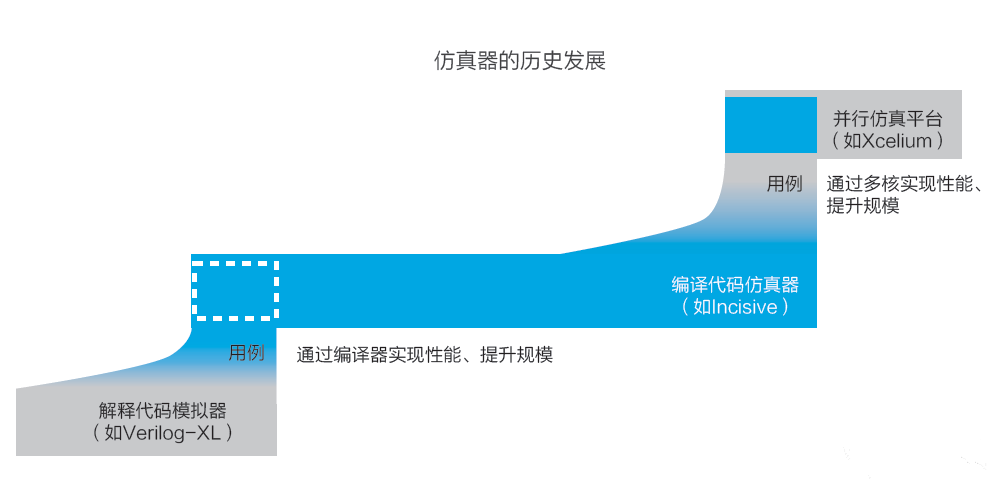

The development history and future trends of chip design simulation technology

The first generation of commercial simulation technology for chip design appeared in the late 1980s, represented by interpreter code simulators such as Verilog-XL and Rapid Sim. Its working mechanism is to compile it into p code first and then interpret and execute it, so the running speed is extremely slow, but it is enough to cope with the small design at that time.

As the design scale slowly increased, compiled code simulators appeared in the mid-1990s to meet the design requirements for speed and capacity. Its working principle is to convert the source code into machine code before running the simulation. This is the second generation of simulation technology, the development is more complicated, it took about three years to realize the support for the language and use model simulation at that time. Since then, the second-generation simulator has been the mainstream simulator in the industry, and has realized support for multiple new standards such as e, SystemC, SystemVerilog, CPF and UPF.

However, as chip design sizes become larger and more complex, the second-generation simulation technology has been unable to meet market demands. Today's SoCs generally include multi-core designs with more than one million gates, and testing these chips may take several weeks. Fortunately, in order to adapt to the increase in SoC size and complexity, simulation technology is also developing rapidly. Parallel simulation that has recently appeared is just such a technology that improves the efficiency of verification by speeding up the test.

Figure 3: The development of three generations of simulation technology

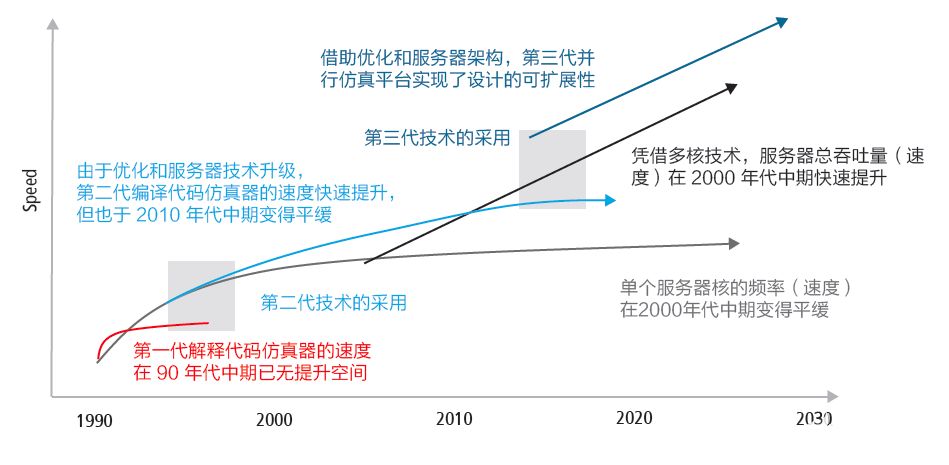

The Xcelium parallel simulation platform launched by Cadence supports standard multi-core servers (up to 64 cores) and adopts fine-grained multi-process technology, which can decompose the simulation running on the compiled code simulation platform into two parts that can be accelerated and not. The parts that can be accelerated (such as gate-level logos or SystemVerilog RTL parts) are processed by the parallel engine, and the verification engineer does not need to change the test platform, design or assertion. Xcelium operates at the language level, so it does not depend on process nodes, and it does not matter whether the design is a CPU, a processor, or a data path design. In addition, the design level will not have an impact.

Figure 4: The third generation of parallel simulation technology will become the mainstream in the next 20 years

The first two generations of simulation technology have each developed for about 20 years. We have reason to believe that the new parallel simulation technology will become the simulation foundation for the next 20 years.

appendix

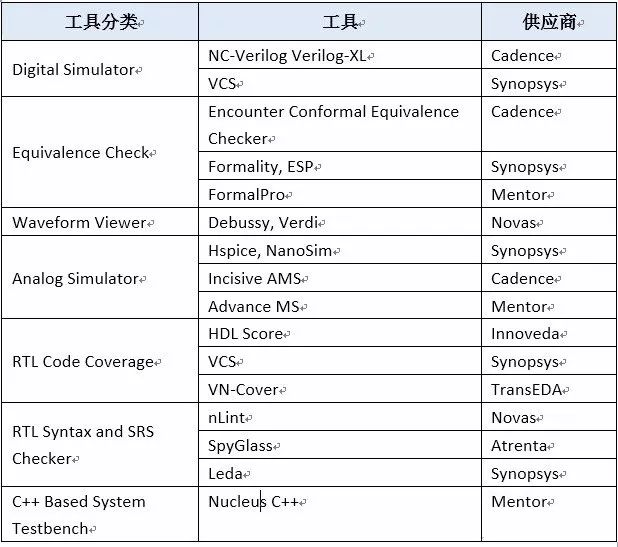

Main simulation and verification tools in SoC design

The three major EDA suppliers can provide a complete set of chip design solutions, including a complete set of design tools such as analog, digital front-end, back-end, DFT, and Signoff. Cadence's strengths lie in analog and mixed-signal simulation and layout design, but its Signoff tools are weak. Synopsys's advantages are digital front-end, digital back-end and PTsignoff, while Mentor's advantages are Calibre signoff and DFT.

In addition, Candence and Synopsys also provide IP licensing (hard core and soft core), which is very attractive to small and medium-sized design companies. Authorized IP usually has hard cores with relatively high R&D costs or thresholds such as memory, Serdes, and Power management.

The following table lists some of the main simulation and verification tools commonly used in SOC design for your reference.

Yacenter hook-up wire and lead wire is manufactured to strict industry specifications. Our collection of hook-up wire and lead wire may be applied for electronic use where high temperatures are encountered. PTFE Coated hook-up wire possesses excellent resistance to thermal aging, solder iron damage, flame, and moisture. Allied Wire offers electrical wire in a range of insulating materials, colors and sizes. Insulating materials include PVC, Irradiated PVC, Irradiated Polyolefin and PTFE. AWC hook-up wire products efficiently answer marketplace demands.

Lead Wire,Balloon Detonator Wire,Ph Connector Harness,Fan Wiring Harness

Dongguan YAC Electric Co,. LTD. , https://www.yacentercns.com