Abstract: This paper mainly introduces the design of data buffer and signal format conversion in the case of multi-channel video signal input in video surveillance board, and uses Altera's Cyclone device to realize the whole process. This includes a brief introduction to the principle of the video monitor board, the role and status of this switching logic in the system, and a detailed description of the process that this logic uses for FPGA design.

This article refers to the address: http://

With the rapid development of technology, the video surveillance market has also developed rapidly. Video surveillance is widely used in many applications because of its intuitiveness, convenience, and rich information content. In recent years, with the widespread use of the Internet and the rapid development of computers, networks, and image processing and transmission technologies, video surveillance technology has also made great progress. Video surveillance has penetrated into education, government, entertainment venues, hospitals, hotels, sports venues, urban security and other fields. Video surveillance servers are called another consumer electronics product with great market prospects after mobile phones.

The digital network video monitoring server mainly completes the function of sending the analog signal obtained from the camera to the digital compression and then sending it to the network. The principle block diagram is shown in Figure 1.

Figure 1 Digital network video surveillance server block diagram

As shown in FIG. 1, the monitor circuit board is mainly composed of an A/D chip, an FPGA multiplexer chip, a compression chip, a CPU, and the like. The FPGA implementation of the multiplexed logic to be introduced in this paper is located between the A/D chip and the compression chip. Since the PLL module is included in the FPGA, the 27MHz input clock of the TW2804 chip connected to the FPGA can be generated by the FPGA.

Here we choose Altera's Cyclone series EP1C6Q240C8, which has 90k storage capacity inside, 6kLEBS, 2 PLLs. In the later design introduction, we will talk about the entire design using 64k storage capacity, 1 PLL, about 4— LEBS around 5k, so this low-cost FPGA can be used to complete this design, and basically use most of the internal resources, plus 240 pins of this chip, can meet the external pin connection, so Altera's EP1C6Q240C8 is the best choice for this logic design.

As shown in Figure 1, the A/D chip accepts four analog video signals from four cameras. Here, Techwell's TW2804 chip is used. This chip supports the input of four video analog signals. The output is digital ITU-R BT.656. The format of the signal, the clock is 27MHz. The timing diagrams of the D1, D2, D3, and D4 signals are shown in Figure 2.

Figure 2 ITU-R BT.656 format signal timing diagram

The EAV and SAV are the line end and line head flag signals respectively. The middle of them is the blank signal between the lines. The signal after the VALID after the SAV is valid is 1440 bytes of the effective video signal in the d1 format. The total of these signals is added up. One line of video signal, one frame of video signal includes 576 lines of line signals, that is, a frame of output video signal of this format is 1440*576 bytes, since each line of signals is represented by two bytes. Pixels, so this d1 format has a pixel of 720*576 resolution.

The function of the FPGA transfer logic is to display four channels of video signals simultaneously on the display terminal. That is, the video signal as shown in FIG. 3 is to be displayed.

Since four signals are simultaneously displayed on one display terminal, the original 720*576 resolution of each signal is converted to the original 1/4 resolution, that is, the cif format, and the cif format is the resolution of 352*288. The signals of the four-way cif format are combined into a frame output as shown in FIG. 3 and displayed to the terminal.

Because the terminal display requires four channels of video signals to be output synchronously, that is, one of the signals is not allowed to be displayed on the display, but another signal has not been displayed, that is, a part of the screen is black. Therefore, in this case, four different video signals need to be buffered in the SDRAM by the FPGA first. When each signal is at least one frame in the SDRAM, it can be read synchronously and passed through the FPGA. The cache is composed of the frame format shown in Figure 3, and then output to the compression chip for compression and then controlled by the processor to output to the network. Here, the compression chip is selected by VWEB's VW2010.

Figure 3 shows the terminal video signal format

At this point, the function to be implemented by the FPGA has been very clear. First, the input four-channel d1 format signals are respectively converted into four-way cif format signals, and then the four signals are respectively buffered in the SDRAM, when each signal in the SDRAM is When at least one frame is stored, the data is read out synchronously, and after the SDRAM is read into the FPGA, the format is recombined, and finally the signal format output as shown in FIG. 3 is formed. The cache control of data in SDRAM is the most important and complicated part. The logic design and implementation of this FPGA is described in detail below.

As can be seen from the above description, this FPGA mainly has three interfaces, the input interface of TW2804, the cache interface of SDRAM, and the output interface of VW2010. So the internal logic of the FPGA can be roughly designed as shown in Figure 4.

Figure 4 FPGA internal logic block diagram

The input format conversion module mainly performs conversion of four signals from d1 to cif format, that is, from the original resolution of 720*576 pixels to the resolution of 352*288 pixels. The conversion process is to remove all the data of even rows in a frame, and each row is removed one by one in the order of pixels, and the last retained data is the original 1/4 of the data. This process is relatively simple and can be achieved by designing two row and column counters. The simulation diagram is shown in Figure 5.

Figure 5 Schematic diagram of simple simulation of d1 to cif format conversion

Figure 5 shows that the data is valid one empty at odd lines. After reading one line, the next line is invalid.

Next is the internal input buffer module, which is used to control the module that is connected to the SDRAM control and performs data buffer control. Its internal logic diagram is shown in Figure 6.

Figure 6 Connection logic diagram of FPGA internal buffer and internal SDRAM controller

The functions that can be extended and improved after this design are given below.

First, because this is a four-way multiplex buffer, they are directly combined and sent to the network display terminal. If you need to support more channels of video signal input for multiplex, for example, the input signal is 8 or 16 channels, then there is a combined problem when sending to the network, that is, the four images on the display finally show the video input. Four. This is also a common situation in actual situations. For example, eight cameras are installed in a building. In the case of daytime, it may be necessary to monitor the situation in the corridor, and in the evening, it may be necessary to monitor the doorway outside the building. It is necessary to make a choice in the FPGA, so at this time, an I2C slave module can be added to the FPGA, through which the module can communicate with the processor, and some registers are set in the FPGA through different register configuration commands sent by the I2C. , real-time switching of images on the display can be achieved.

Secondly, due to the limited storage capacity of the Cyclone series, if you want to increase the size to 16 channels, the input and output buffer storage capacity will not be enough, so you can consider the Cyclone2 series products.

In addition, if you want to complete the transfer of more roads in the future, you can add a few more TW2804 and VW2010 chips on the monitor board, so you need more FPGA input and output pins, and there are 240 FPGA chips like EP1C6Q240C8. Pins are needed for expansion.

In summary, Altera's Cyclone series of low-cost FPGA products are used in such switching logic, making full use of its existing internal resources, and the price is very easy to accept, is an ideal choice.

This design project was independently designed and implemented by the author at the Longxin Industrialization R&D Center as a guest graduate student. The CPU of the video monitor is Loongson No. 2, and the transfer logic has been successfully designed.

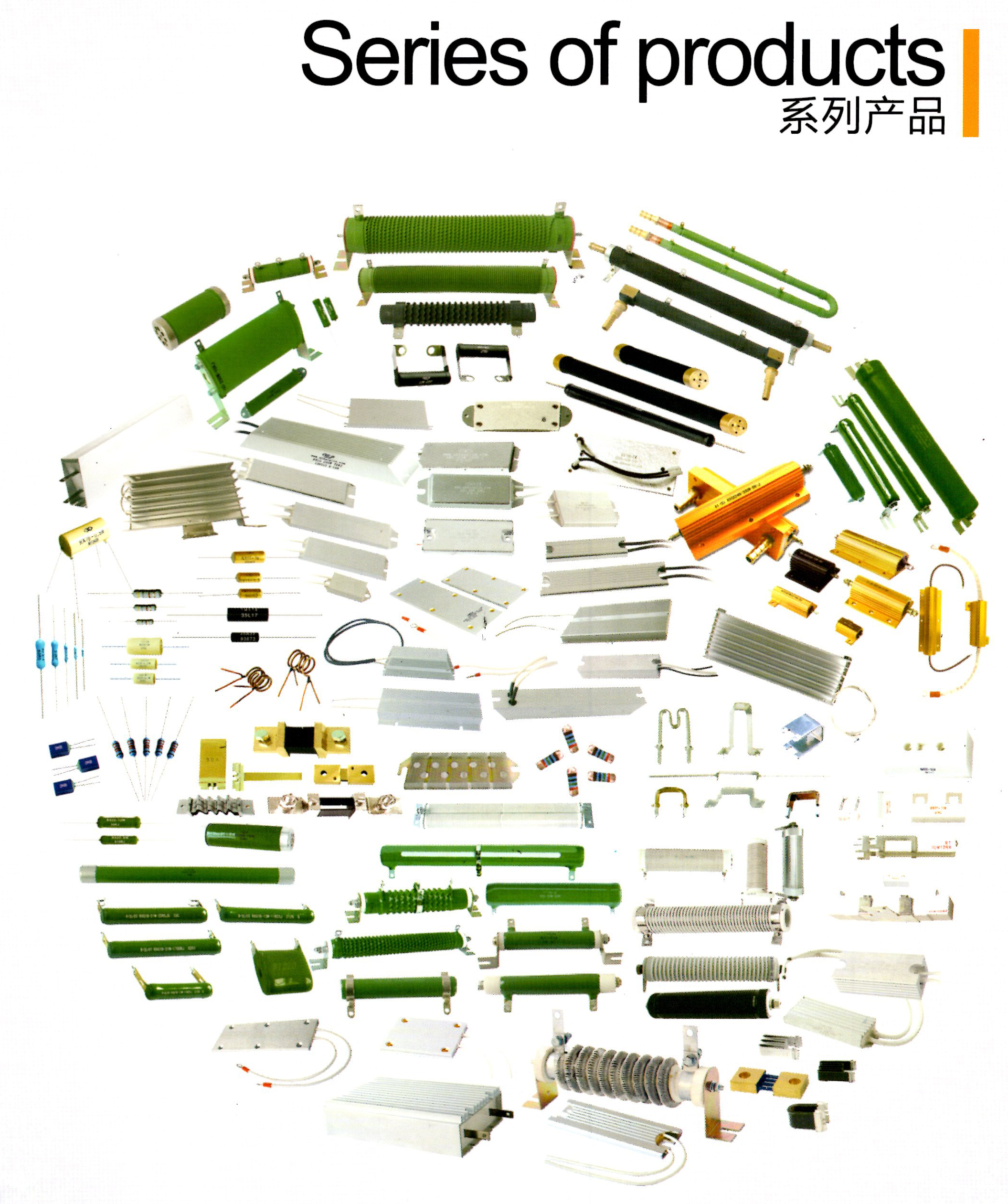

Electronic Components Resistor

Resistor (Resistor) commonly known as resistance directly in our daily life.It is a current limiting element. When the resistance is connected to the circuit, the resistance value of the resistor is fixed, usually two pins.Fixed resistors are those whose resistances cannot be changed.Resistance variable is called potentiometer or variable resistor.The ideal resistor is linear, that is, the instantaneous current through the resistor is proportional to the applied instantaneous voltage.Variable resistor for partial pressure.On the exposed resistor body, one or two movable metal contacts are pressed tightly.The contact position determines the resistance between any end of the resistance body and the contact.

Flat tube resistor

Metal aluminum shell resistor

Stainless steel resistor box

Crowbar (wind power converter) resistor

RX21 Glazed Wirewound Resistor

RX21 Glazed Power Wirewound Resistor

Inverter ceramic resistor

Resistor Cabinet

Resistive load box

Ultra-thin aluminum shell resistor

High power resistor

water cooling resistor

RI80 high voltage resistor

RX20 High Power Painted Wirewound Resistor

stainless steel resistor

Howo resistor

KNP Porcelain Rod Painted Wirewound Resistor

Cement Resistor

Thick Film Resistors

Electronic Components Resistor,Metal Film Resistor,Metal Oxide Film Resistor

YANGZHOU POSITIONING TECH CO., LTD. , https://www.yzpst.com